| DuneNvme 1.0.2 This is a simple NVMe test environment that allows experimentation with the low level PCIe NVMe interfaces as available on a Xilinx FPGA environment. |

AxisDataConvertFifo Entity Reference

AXI Stream data Fifo with conversion from 256 to 128 bits. More...

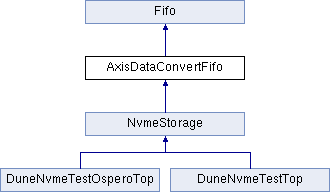

Inheritance diagram for AxisDataConvertFifo:

Entities | |

| Behavioral | architecture |

Libraries | |

| ieee | |

| work | |

Use Clauses | |

| std_logic_1164 | |

| numeric_std | |

| NvmeStoragePkg | Package <NvmeStoragePkg> |

| NvmeStorageIntPkg | Package <NvmeStorageIntPkg> |

Generics | |

| Simulate | boolean := False |

| Enable simulation core. | |

| FifoSizeBytes | integer := NvmeStorageBlockSize |

| The Fifo size in bytes. | |

Ports | ||

| clk | in | std_logic |

| Module clock. | ||

| reset | in | std_logic |

| Module reset line. Clears Fifo. | ||

| streamRx | in | AxisDataStreamType |

| Input data stream. | ||

| streamRx_ready | out | std_logic |

| Ready signal for input data stream. | ||

| streamTx | inout | AxisStreamType := AxisStreamOutput |

| Output data stream. | ||

Detailed Description

AXI Stream data Fifo with conversion from 256 to 128 bits.

- Date

- 2020-05-15

- Version

- 1.0.0

This module accepts an AxisDataStreamType AXI4 type data stream with 256 bit width data. It performs a Fifo function outputing the data on a 128 bit wide AxisStreamType AXI4 type stream. The last signal is passed through the Fifo. The FIFO depth is configurable with the FifoSizeBytes parameter which is in Bytes. For the NvmeStorage system this is normally set to the block size of 4096 Bytes. The modules uses block RAM to store the data.

- Copyright

- 2020 Beam Ltd, Apache License, Version 2.0 Copyright 2020 Beam Ltd Licensed under the Apache License, Version 2.0 (the "License"); you may not use this file except in compliance with the License. You may obtain a copy of the License at http://www.apache.org/licenses/LICENSE-2.0 Unless required by applicable law or agreed to in writing, software distributed under the License is distributed on an "AS IS" BASIS, WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied. See the License for the specific language governing permissions and limitations under the License.

The documentation for this class was generated from the following file:

- /src/dune/source/DuneNvme/src/AxisDataConvertFifo.vhd

Generated by

1.8.15

1.8.15