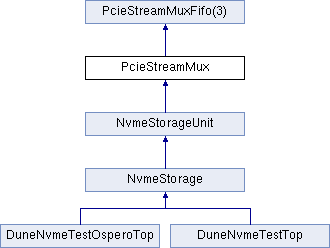

| DuneNvme 1.0.2 This is a simple NVMe test environment that allows experimentation with the low level PCIe NVMe interfaces as available on a Xilinx FPGA environment. |

This module Multiplexes/De-multiplexes a PCIe 128 bit stream into two streams using the 128bit header. More...

Entities | |

| Behavioral | architecture |

Libraries | |

| ieee | |

| unisim | |

| work | |

Use Clauses | |

| std_logic_1164 | |

| numeric_std | |

| vcomponents | |

| NvmeStoragePkg | Package <NvmeStoragePkg> |

| NvmeStorageIntPkg | Package <NvmeStorageIntPkg> |

Generics | |

| RegisterOutputs | boolean := True |

| Register the outputs. | |

Ports | ||

| clk | in | std_logic |

| The interface clock line. | ||

| reset | in | std_logic |

| The active high reset line. | ||

| stream1In | inout | AxisStreamType := AxisStreamInput |

| Single multiplexed Input stream. | ||

| stream1Out | inout | AxisStreamType := AxisStreamOutput |

| Single multiplexed Ouput stream. | ||

| stream2In | inout | AxisStreamType := AxisStreamInput |

| Host Replies input stream. | ||

| stream2Out | inout | AxisStreamType := AxisStreamOutput |

| Host Requests output stream. | ||

| stream3In | inout | AxisStreamType := AxisStreamInput |

| Nvme Requests input stream. | ||

| stream3Out | inout | AxisStreamType := AxisStreamOutput |

| Nvme replies output stream. | ||

Detailed Description

This module Multiplexes/De-multiplexes a PCIe 128 bit stream into two streams using the 128bit header.

- Date

- 2020-04-08

- Version

- 1.0.0

This module will multiplex two bi-directional AxisStream's into a single bi-directional stream and de-multiplex a single bi-directional stream into two such streams. It is used to handle the quad stream nature of the Xilinx Pcie Gen3 hardblock merging the two streams into one for easy processing. The Xilinx Pcie Gen3 IP uses a pair of streams for host requests to the Pcie device (stream2) and a pair of streams for Pcie device requests to the host (stream3). Because of the 4 streams and their usage each will solely transport request or reply packets. This module sets and uses the state of bit 95 in the Pcie request and reply headers when multiplexing/de-muliplexing packets to/from the single stream (stream1). When muliplexing the packets bit 95 is set in the header on any reply packets and when de-multiplexing it looks at bit 95 in the header to determine which stream to send the packet on. The RegisterOutputs parameter allows the output data streams to be latched for better system timing at the expence of a 1 clock cycle latency. the module prioritises packet replies from the Pcie device when multiplexing. The multiplex and de-multiplex processes are separate and function independantly.

- Copyright

- 2020 Beam Ltd, Apache License, Version 2.0 Copyright 2020 Beam Ltd Licensed under the Apache License, Version 2.0 (the "License"); you may not use this file except in compliance with the License. You may obtain a copy of the License at http://www.apache.org/licenses/LICENSE-2.0 Unless required by applicable law or agreed to in writing, software distributed under the License is distributed on an "AS IS" BASIS, WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied. See the License for the specific language governing permissions and limitations under the License.

The documentation for this class was generated from the following file:

- /src/dune/source/DuneNvme/src/PcieStreamMux.vhd

Generated by

1.8.15

1.8.15