| DuneNvme 1.0.2 This is a simple NVMe test environment that allows experimentation with the low level PCIe NVMe interfaces as available on a Xilinx FPGA environment. |

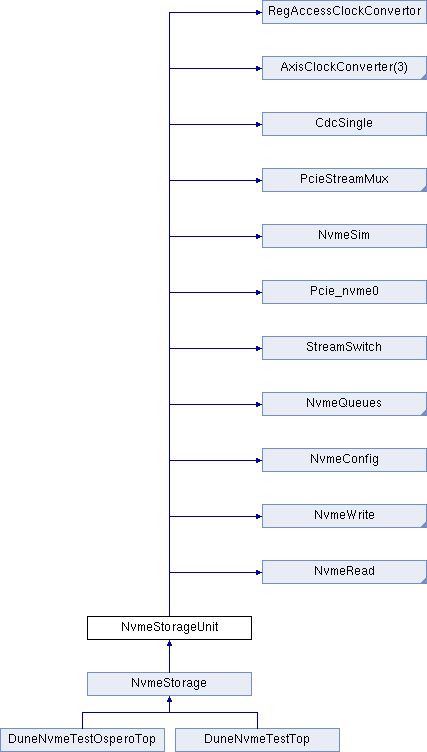

This is the main Nvme control module for a single Nvme device. More...

Entities | |

| Behavioral | architecture |

Libraries | |

| ieee | |

| unisim | |

| work | |

Use Clauses | |

| std_logic_1164 | |

| numeric_std | |

| vcomponents | |

| NvmeStoragePkg | Package <NvmeStoragePkg> |

| NvmeStorageIntPkg | Package <NvmeStorageIntPkg> |

Generics | |

| Simulate | boolean := False |

| Generate simulation core. | |

| Platform | string := " Ultrascale " |

| The underlying target platform. | |

| ClockPeriod | time := 4 ns |

| Clock period for timers (250 MHz) | |

| BlockSize | integer := NvmeStorageBlockSize |

| System block size. | |

| PcieCore | integer := 0 |

| The Pcie hardblock block to use. | |

| UseConfigure | boolean := False |

| The module configures the Nvme's on reset. | |

| NvmeBlockSize | integer := 512 |

| The NVMe's formatted block size. | |

| NvmeTotalBlocks | integer := 104857600 |

| The total number of 4k blocks available (400G) | |

| NvmeRegStride | integer := 4 |

| The doorbell register stride. | |

Ports | ||

| clk | in | std_logic |

| The interface clock line. | ||

| reset | in | std_logic |

| The active high reset line. | ||

| regWrite | in | std_logic |

| Enable write to register. | ||

| regRead | in | std_logic |

| Enable read from register. | ||

| regAddress | in | unsigned ( 5 downto 0 ) |

| Register to read/write. | ||

| regDataIn | in | std_logic_vector ( 31 downto 0 ) |

| Register write data. | ||

| regDataOut | out | std_logic_vector ( 31 downto 0 ) |

| Register contents. | ||

| hostSend | inout | AxisStreamType := AxisStreamInput |

| Host request stream. | ||

| hostRecv | inout | AxisStreamType := AxisStreamOutput |

| Host reply stream. | ||

| dataEnabledOut | out | std_logic |

| Indicates that data ingest is enabled. | ||

| dataIn | inout | AxisStreamType := AxisStreamInput |

| Raw data to save stream. | ||

| nvme_clk | in | std_logic |

| Nvme external clock. | ||

| nvme_clk_gt | in | std_logic |

| Nvme external GT clock. | ||

| nvme_reset_n | out | std_logic |

| Nvme reset output to reset NVMe devices. | ||

| nvme_exp_txp | out | std_logic_vector ( 3 downto 0 ) |

| nvme PCIe TX plus lanes | ||

| nvme_exp_txn | out | std_logic_vector ( 3 downto 0 ) |

| nvme PCIe TX minus lanes | ||

| nvme_exp_rxp | in | std_logic_vector ( 3 downto 0 ) |

| nvme PCIe RX plus lanes | ||

| nvme_exp_rxn | in | std_logic_vector ( 3 downto 0 ) |

| nvme PCIe RX minus lanes | ||

| leds | out | std_logic_vector ( 2 downto 0 ) |

Detailed Description

This is the main Nvme control module for a single Nvme device.

- Date

- 2020-05-12

- Version

- 1.0.0

This module manages a single Nvme device. It is controlled via a simple register access interface and an optional bi-directional PCIe packet stream. An AXI4 data stream, blocked into BlockSize Bytes using the "last" signal, is written sequentially to the Nvme device's blocks. The DataChunkStart and DataChunkSize registers define the starting block number and the number of blocks to write. It accepts a 250 MHz clock input to which all input and output signals are syncronised with. Internally it uses a 250 MHz clock generated from the Nvme devices PCIe clock. The module handles the necessary clock domain crossings for this. The PcieCore parameter defines which Pcie Gen3 IP block to use allowing muliple NvmeStorageUnit's to be used in a design. Note that this is required due to the nature of the Xilinx Pcie Gen3 IP blocks implementation. It would be nice to use a generic Xilinx Pcie Gen3 IP component and set the locations of this in a system constraints file. The Platform parameter is available to handle alternative Pcie hard block interface types. The UseConfigure parameter sets the system to automatically configure the Nvme device on reset. Parameters for the actual Nvme device in use need to be set in the NvmeBlockSize, NvmeTotalBlocks and NvmeRegStride parameters. See the NvmeStorageManual for more details.

- Copyright

- 2020 Beam Ltd, Apache License, Version 2.0 Copyright 2020 Beam Ltd Licensed under the Apache License, Version 2.0 (the "License"); you may not use this file except in compliance with the License. You may obtain a copy of the License at http://www.apache.org/licenses/LICENSE-2.0 Unless required by applicable law or agreed to in writing, software distributed under the License is distributed on an "AS IS" BASIS, WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied. See the License for the specific language governing permissions and limitations under the License.

The documentation for this class was generated from the following file:

- /src/dune/source/DuneNvme/src/NvmeStorageUnit.vhd

Generated by

1.8.15

1.8.15